Вилкинсон көч бүлгечекөч бүлүче схема. Барлык портлар туры килгәндә, ул ике чыгыш порты арасында изоляцияне гамәлгә ашыра ала. Wilkinson көч бүлүчесе теләсә нинди көч бүленешен гамәлгә ашырырлык итеп эшләнсә дә (мәсәлән, Pozar [1] карагыз), бу мисалда тигез бүленеш (3дБ) очрагы өйрәнеләчәк. FDTD җайланманың таралу параметрларын алу өчен кулланылачак.

Вилкинсон көч бүлгечеАналог көйләүләре

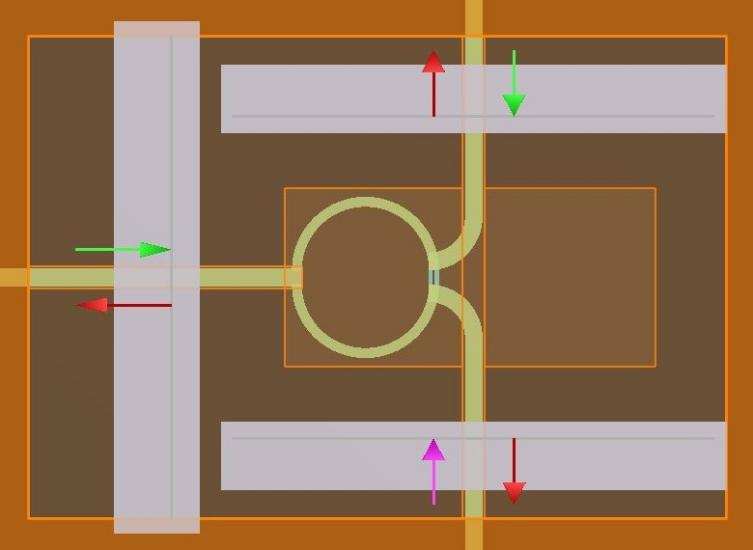

"Эзләү һәм йөкләнеш" структура төркеме Wilkinson_ power_ divider FDTD симуляция файлында кулланыла. Wilkinson көч бүлгеченең физик һәм электр параметрлары fsp форматында төзелгән һәм урнаштырылган. Микрополосалы тапшыру линиясе 1,59 мм калынлыктагы субстратка урнаштырылган ике үлчәмле камил электр үткәргеч (PEC) турыпочмаклы пластина ярдәмендә модельләштерелгән, аның чагыштырма диэлектрик даимилеге 2,2 тәшкил итә. Һәр тапшыру линиясе кисемтәсенең кирәкле киңлеге тигезләмә ярдәмендә исәпләнә. Pozar [1] 3.195 һәм 3.197 (микрополоса мисалындагы microstrip.lms скрипт файлын карагыз) 4,9 мм (Z0=50 ом) һәм 2,804 мм (√ 2Z0=70,7 ом) тәшкил итә. Чирек дулкын озынлыгы тапшыру линиясе боҗрага формалаштырылган 2D күппочмаклар ярдәмендә төзелгән. Позарда [1] 3.194 λ g/4=55.5 мм тәшкил итә. Резистор R=100 Ом булган материалны күрсәтүче 2D турыпочмаклы пластина ярдәмендә модельләштерелгән.

Портлар 0,5 – 1,5 ГГц ешлык диапазонында тапшыру линиясе режимын кертү һәм җиһазларның таралу параметрларын исәпләү өчен керү һәм чыгу юлларына урнаштырыла. Аның көйләүләре турында тулырак мәгълүмат өчен "Портлар" битен карагыз. Түбәндә тасвирланганча, чыганак порты берьюлы бер портны эшләтер өчен кул белән үзгәртеләчәк.

Сетка каплау мәйданы һәр юлның озынлыгын һәм киңлеген билгеләү өчен урнаштырыла. Тармак эзенең бөкләнү һәм почмак үзенчәлекләре x һәм y юнәлешләрендә челтәр зурлыгының тигез булуын таләп итә (dx=dy). Бу координата күчәренә туры китерелгән туклану һәм чыгу юллары өчен чикләү түгел. Симметрик челтәрне саклап калу өчен тармак эзе каплау мәйданының күчермәсе чыгу эзенең уң ягына урнаштырыла.

PML сеңү чиге шарты, микрополосалы тапшыру линиясенең җирләү яссылыгын симуляцияләүче металл чик шарты буларак билгеләнгән z-минимум чигеннән кала, симуляция өлкәсенең барысын да уратып ала.

Вилкинсон көч бүлгече Нәтиҗәләр һәм анализ

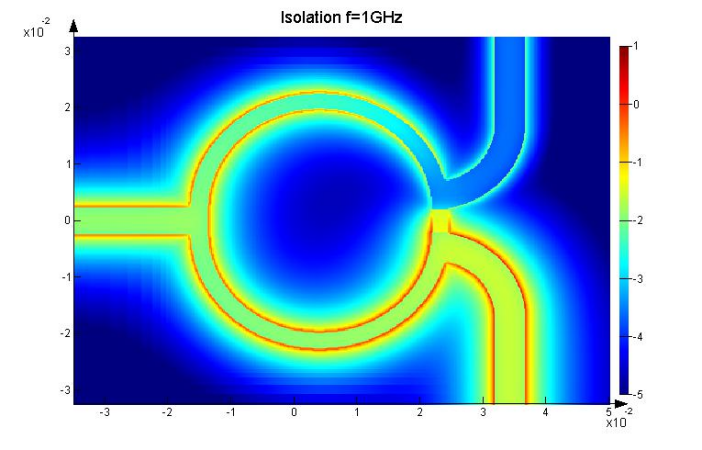

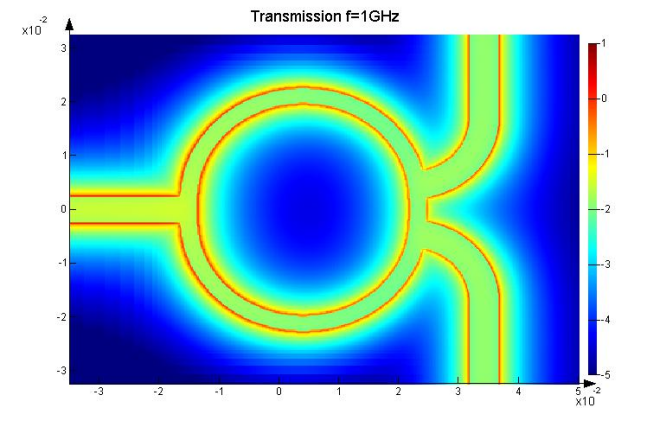

Югарыдагы рәсемдә изоляция һәм тапшыру симуляциясе өчен кулланылган таралу параметрларының ешлык реакциясе һәм 1 ГГц ешлыктагы электр кыры бүленеше күрсәтелгән. Бу саннар симуляция тәмамланганнан соң скрипт ярдәмендә барлыкка килә. Шунысын да билгеләп үтәргә кирәк, бу нәтиҗәләрне симуляция файлында күрсәтелгәннәргә караганда нечкәрәк челтәрләр кулланып траекториядә алырга мөмкин.

АналогВилкинсон көч бүлгечекерү (S11=- 40дБ, f=1.0GHz) һәм чыгу (S22=- 32дБ, f=1GHz) портларында яхшы туры килә, яхшы изоляциягә ия (S32=- 43дБ, f=1GHz), һәм аның үзәк ешлыгы 1.01ГГц, бу 1ГГц эш ешлыгының 1% эчендә. Моннан тыш, без аналог ешлык диапазонында 10% тан ким үзгәреш белән 3дБ тигез көч бүленешен (f=1ГГцда S31=- 3дБ) күзәттек.

Si Chuan Keenlion микродулкынлы мичләре тар диапазонлы һәм киң полосалы конфигурацияләрдә зур сайлау тәкъдим итә, 0,5 дән 50 ГГц га кадәр ешлыкларны үз эченә ала. Алар 50 Ом тапшыру системасында 10 нан 30 ватт га кадәр керү көчен эшкәртер өчен эшләнгән. Микродиапазонлы яки тасмалы конструкцияләр кулланыла һәм иң яхшы эшләү өчен оптимальләштерелә.

Шулай ук без сезнең таләпләрегезгә туры китереп, көч бүлгечен көйли алабыз. Сез кертә аласызкирәкле спецификацияләрне бирү өчен көйләү бите.

Сычуань Кинлион микродулкынлы технологияләр компаниясе, ҖЧҖ

Электрон почта:

sales@keenlion.com

tom@keenlion.com

Бастырылган вакыты: 2022 елның 6 декабре